PUSCH Channel IP

Full PUSCH Receiver Chain – 3GPP Complaint Performance

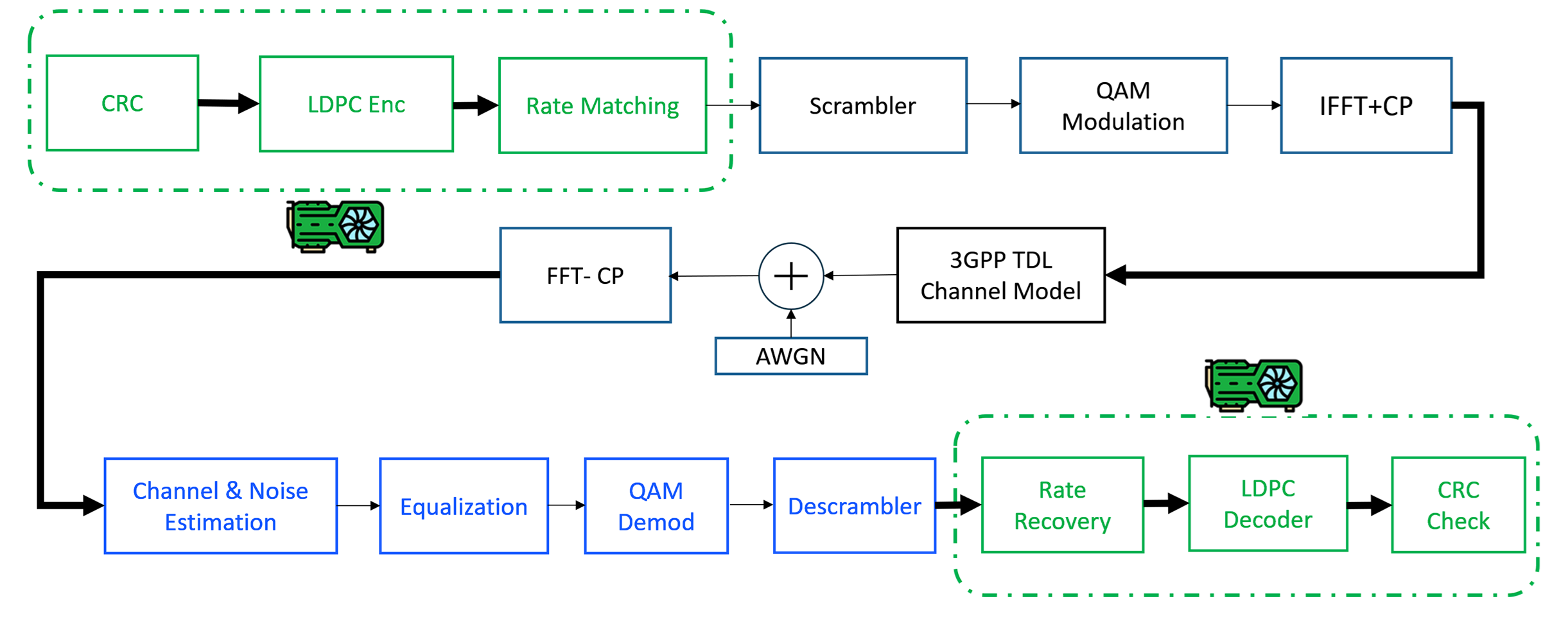

The Physical Uplink Shared Channel (PUSCH) in 5G NR is designated to carry multiplexed control information and user application data. PUSCH receiver is a critical component in the 5G NR uplink chain which needs to be carefully designed to successfully recover data from a noisy and fading wireless channel. Channel estimation, Equalization, Soft Demodulator, Rate recovery and LDPC decoder are major blocks to be highly optimized for throughput, latency, and error rate (BLER) as per 3GPP 38.104 Chapter 8 Performance requirements.

To recover uplink data effectively, the following key processing blocks are of great importance:

Channel Estimation: 4G5G’s channel estimation uses DMRS (Demodulation Reference Signals) embedded in the PUSCH to estimate the radio channel using Least Squares method followed by FFT based Channel interpolation and smoothing. This implementation allows us to offload FFT for GPU acceleration or use traditional efficient software FFT implementation running on CPU cores.

Equalization: MMSE Equalizer is implemented to compensate for channel-induced distortion, including multipath fading. Our implementation handles single layer Tx and 2/4 Rx configurations effectively.

Soft Demodulation

- Converts received QAM symbols into 8 bit LLRs (Log-Likelihood Ratios).

- Supports various modulation schemes (QPSK, 16QAM, 64QAM).

- Our LLR calculation incorporates estimated noise variance and channel gain.

Rate Recovery

- Complete support for puncturing, repetition, and shortening.

- Fully integrated with HARQ buffer management.

- Supports up to 16 HARQ processes and 64 user pers HARQ ID (configurable).

- Supports both GPU Acceleration and CPU Core

LDPC Decoder

- Compliant with 3GPP TS 38.212.

- Supports Base Graphs BG1 and BG2.

- Supports all Code rates and Block sizes corresponding to possible lifting sizes.

- Supports both GPU Acceleration and CPU Core.

Platform-Agnostic PUSCH Receiver for COTS ARM/x86 Servers

- Single Codebase for both ARM and x86 architectures – Fixed point implementation.

- Optimized Algorithms leveraging the Google Highway Project.

- Channel Estimation and Full Bit-Level Processing accelerated on COTS GPUs.

- Complete Software-Only Implementation also available for flexibility and testing.

This solution ensures maximum portability, performance, and ease of integration across diverse commercial off-the-shelf (COTS) platforms.

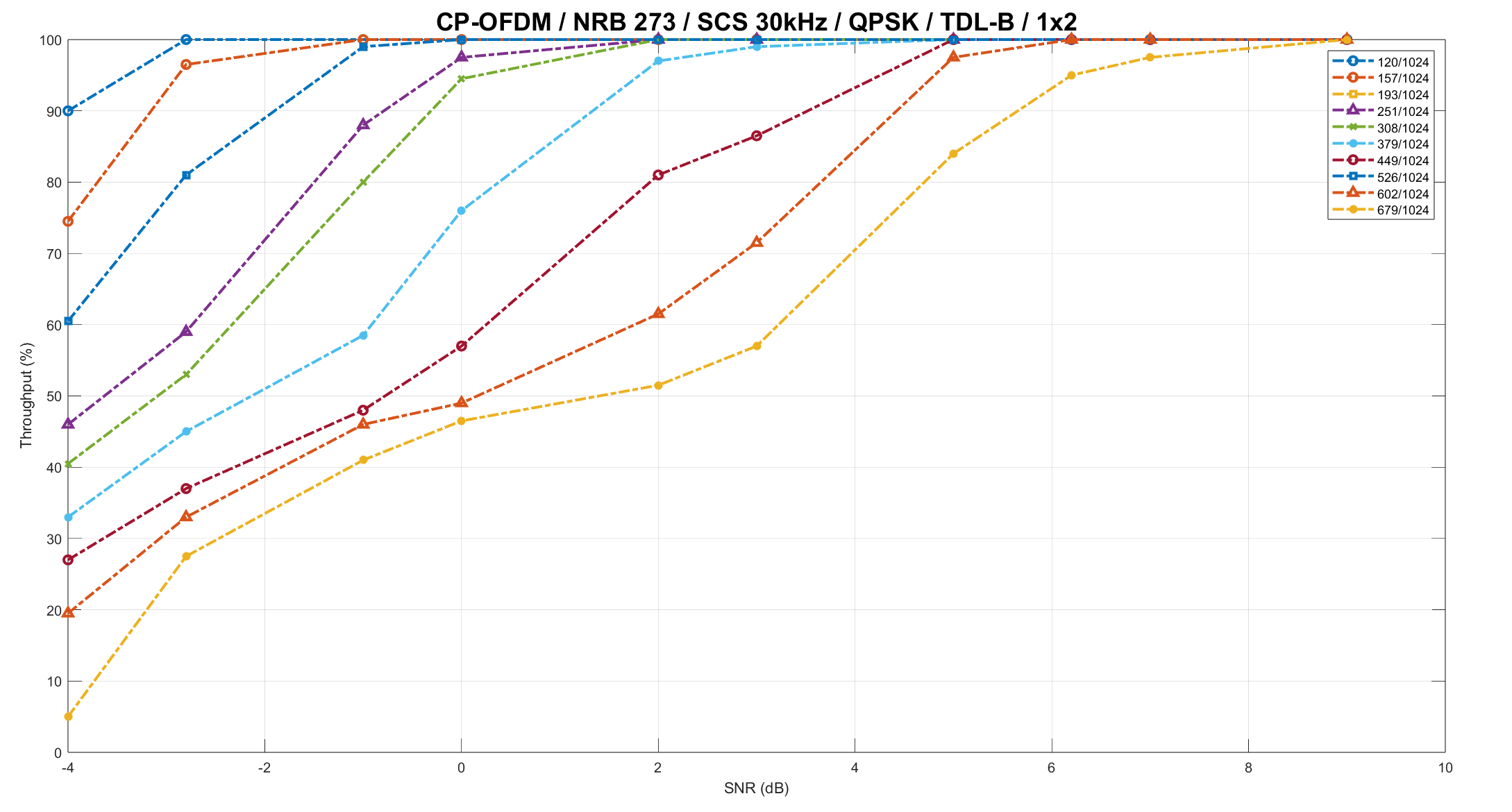

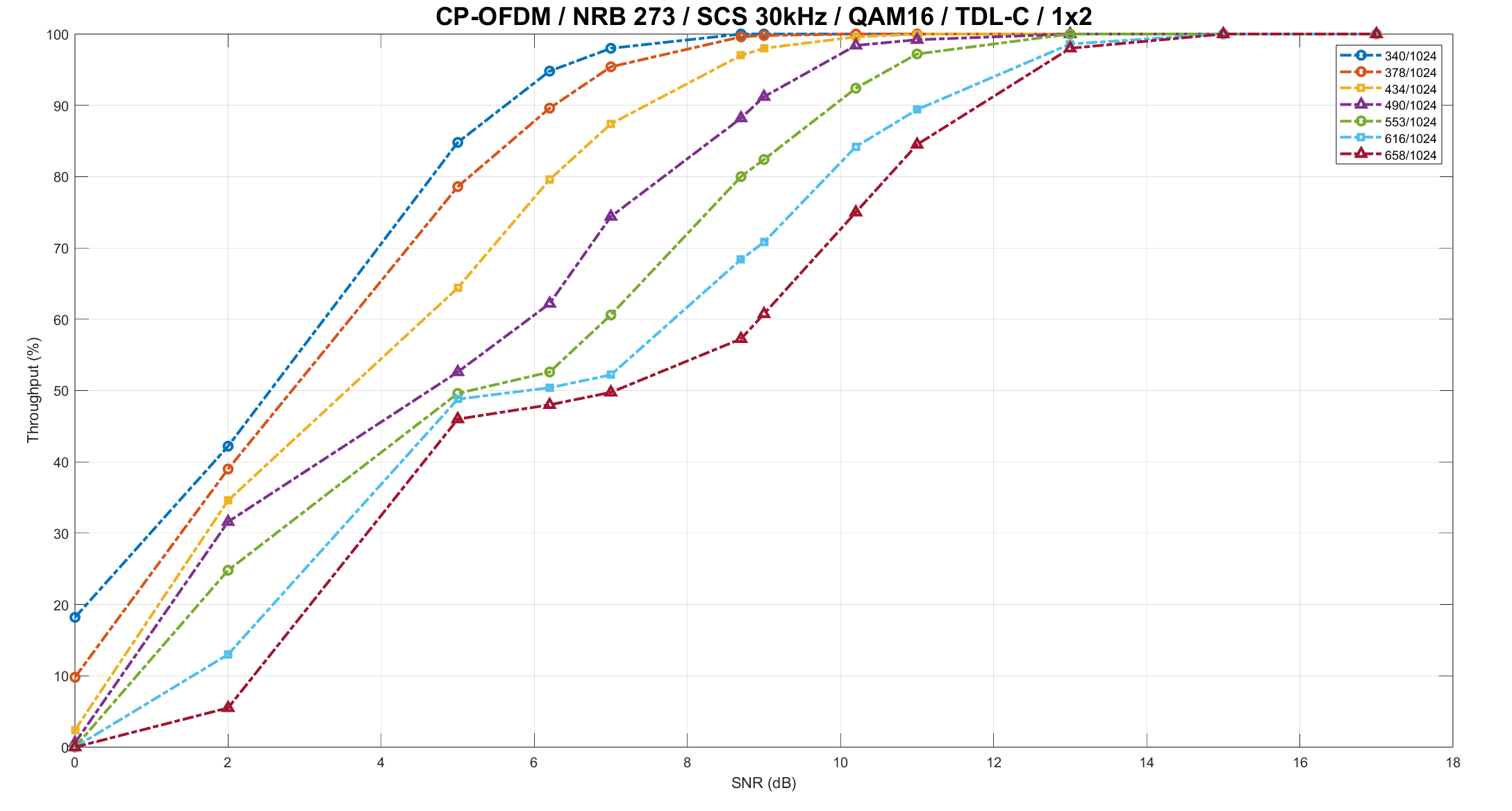

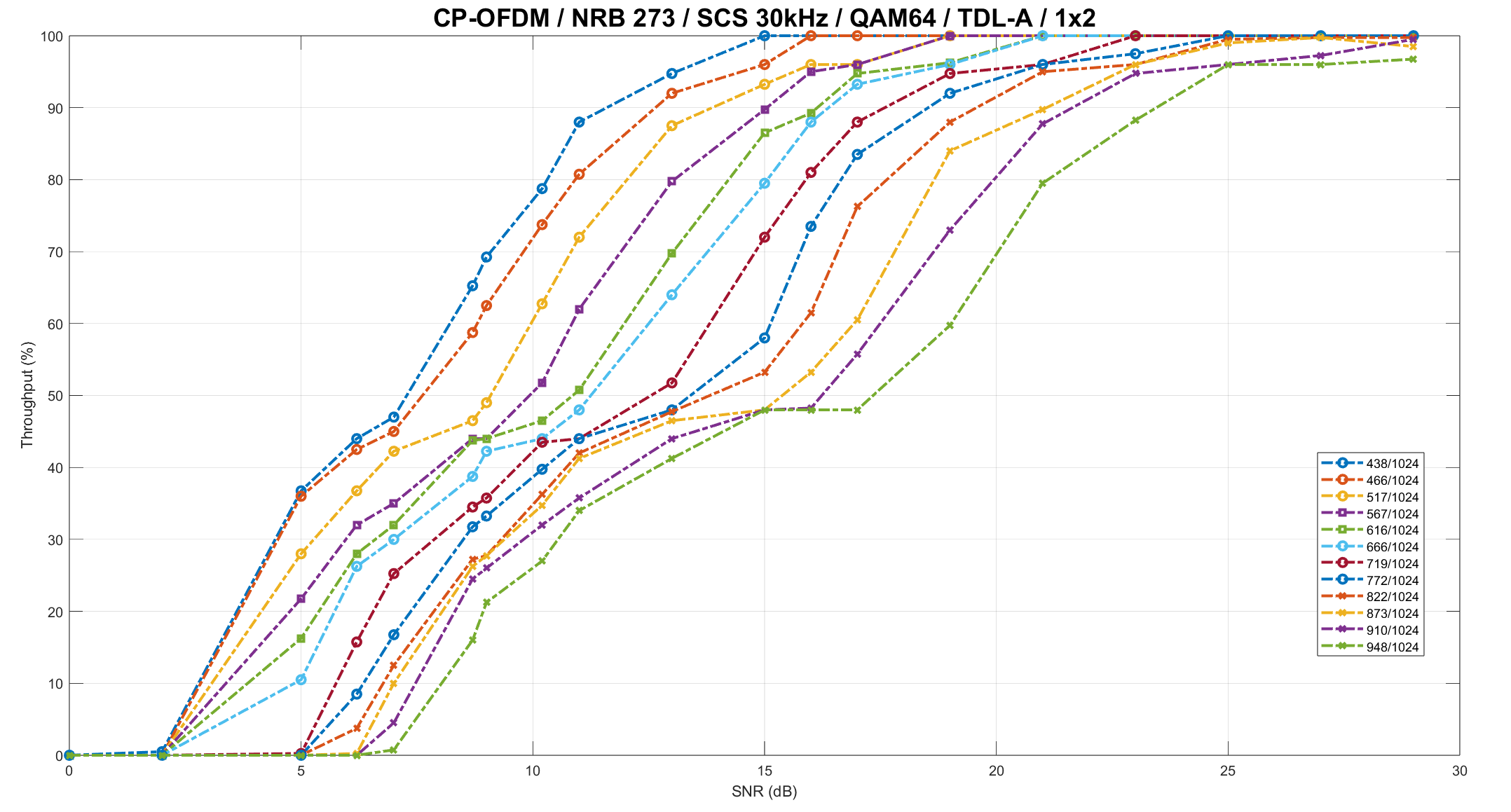

Our PUSCH receiver chain meets 3GPP 38.104 Chapter 8 Performance requirements and below are throughput performance metrices for modulation and code rates as per 3GPP 38.214 Table 5.1.3.1-1: MCS table